在嵌入式系統與信號處理領域,高速實時的數據采集與處理一直是技術挑戰的核心,傳統上,現場可編程門陣列(FPGA)因其并行處理能力、低延遲和可定制硬件邏輯,成為許多高性能應用的默認選擇。隨著半導體技術的飛速發展,新一代系統級芯片(SoC)正以其強大的集成能力和靈活的軟件可編程性,向這一傳統格局發起挑戰。一個引人矚目的觀點開始流傳:有了某款先進的SoC,高速實時的數據采集與處理或許不再需要依賴FPGA了。這是技術演進帶來的現實,還是過于樂觀的預言?

SoC的崛起:集成與軟件定義的力量

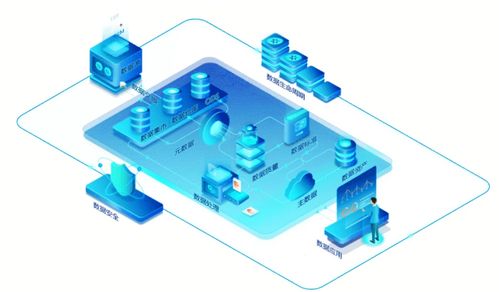

現代高端SoC,特別是那些集成了多核CPU(如Arm Cortex-A系列)、高性能GPU,以及關鍵專用硬件加速模塊(如數字信號處理器DSP、圖像信號處理器ISP、專用AI加速核NPU)的芯片,其綜合算力已今非昔比。它們的核心優勢在于“集成”與“軟件定義”。

- 高度集成:一顆芯片內融合了計算、控制、協處理等多種單元,減少了板級空間和系統復雜度。

- 軟件靈活性:主要功能通過軟件開發實現,迭代更新快,開發工具鏈(如成熟的C/C++、Python環境及豐富的庫)對軟件工程師更為友好,降低了開發門檻和周期。

- 專用硬件加速:針對特定負載(如FFT、卷積計算、編碼解碼)的硬核模塊,能以接近硬件級的效率執行任務,顯著提升實時處理能力。

對于許多中高速、算法復雜度高但數據流相對規整的應用場景(如智能視覺檢測、頻譜分析、一定規模的傳感器融合),一款設計精良的SoC確實能夠獨立勝任,通過高效的軟件調度和硬件加速單元協同工作,滿足實時性要求。

FPGA的不可替代性:并行、確定性與極致定制

盡管SoC進步顯著,但FPGA在極端性能需求場景下依然擁有堅固的壁壘,這源于其底層架構的根本差異:

- 真正的硬件級并行:FPGA可以配置成數百甚至上千個并行處理流水線,同時處理大量數據流,這對于超高速數據流(如雷達信號、高速通信協議)的實時預處理至關重要。SoC的并行性受限于核心數量和架構。

- 納秒級確定性與低延遲:FPGA的邏輯電路運行具有極強的時間確定性,延遲可精確預測和控制。而基于處理器核和操作系統的SoC,其任務調度、中斷響應受軟件影響,存在微秒級甚至更高的抖動,對于要求絕對實時控制(如工業運動控制、高速閉環系統)的應用可能是致命缺陷。

- 比特級硬件定制:FPGA允許設計者創建完全符合特定接口協議、算法或控制邏輯的硬件電路,靈活性無與倫比。SoC的接口和加速器通常是固定或半定制的。

現實路徑:融合與分工,而非簡單替代

因此,“不再需要FPGA”的論斷過于絕對。更準確的技術趨勢是 “分工優化”與“異構融合”。

- SoC主導的領域:對于實時性要求相對寬松(如毫秒級)、算法復雜、需要高級智能處理(如AI推理)且數據速率在SoC接口與處理能力范圍內的應用,使用高性能SoC可以簡化系統設計、降低成本并加速上市。軟件開發的高效性是其最大魅力。

- FPGA依然關鍵的領域:在需要超高速(GHz采樣率)、極低延遲、嚴格確定性時序,或接口協議非常特殊、標準處理器無法直接處理的場景,FPGA仍是無可爭議的選擇。

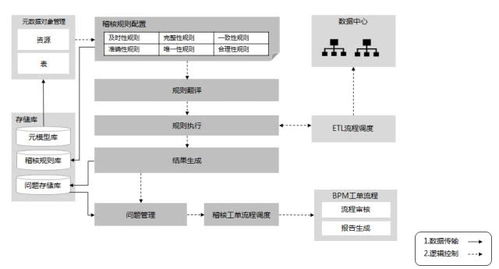

- 強強聯合的異構架構:這正是許多尖端系統的現狀。例如,采用“FPGA + SoC”的架構,讓FPGA負責最前端的高速數據采集、濾波和協議轉換,將預處理后的數據通過高速接口(如PCIe)傳遞給SoC進行復雜的軟件算法分析、決策和上層應用處理。這種架構結合了兩者優點,實現了性能與靈活性的最大化。

結論

聲稱一款SoC就能完全取代FPGA在高速實時數據采集與處理中的所有角色,目前來看尚不現實。這更像是技術演進光譜上的一個動態平衡點。對于開發者而言,關鍵在于精準評估項目需求:明確數據速率、延遲上限、確定性要求、算法復雜性以及成本與開發周期約束。

SoC的進步,特別是其不斷增強的硬件加速能力和軟件生態,正在不斷拓寬其獨立應用的邊界,讓許多以往必須使用FPGA的中等要求應用得以“軟化”。它極大地提升了軟件開發的地位,使得通過精良的軟件設計挖掘硬件潛力變得前所未有地重要。在追求性能極致的領域,FPGA的硬件并行和確定性優勢依然屹立不倒。二者更可能長期共存、協同演進,在不同的細分領域和系統層級中扮演最適合自己的角色,共同推動數據采集與處理技術向前發展。